# Lecture 15 Analysis of Combinational Circuits

# **Designing Combinational Logic Circuits**

A logic circuit having 3 inputs,

A, B, C will have its output HIGH only when a majority of the inputs are HIGH.

<u>Step 1</u> Set up the truth table

<u>Step 2</u> Write the AND term for each case where the output is a 1.

| в | С                          | x                                                                                                                             |                                                       |

|---|----------------------------|-------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------|

| 0 | 0                          | 0                                                                                                                             |                                                       |

| 0 | 1                          | 0                                                                                                                             |                                                       |

| 1 | 0                          | 0                                                                                                                             |                                                       |

| 1 | 1                          | 1 -                                                                                                                           | $\rightarrow \overline{ABC}$                          |

| 0 | 0                          | 0                                                                                                                             | <u></u>                                               |

| 0 | 1                          | 1 -                                                                                                                           | $\rightarrow ABC$                                     |

| 1 | 0                          | 1 -                                                                                                                           | $\rightarrow AB\overline{C}$                          |

| 1 | 1                          | 1 -                                                                                                                           | $\rightarrow ABC$                                     |

|   | 0<br>0<br>1<br>1<br>0<br>0 | 0   0     0   1     1   0     1   1     0   0     1   1     1   0     1   0     1   0     1   0     0   0     1   0     1   0 | $\begin{array}{c ccccccccccccccccccccccccccccccccccc$ |

#### Sum-Of-Products Form

- SOP is useful in simplification and design

- Two or more AND terms OR together –Ex: ABC+ABC

- -the inversion sign cannot cover more than one variable (ABC)

- Another general form for logic expressions is sometimes used in logic-circuit design. It called product-of-sum (POS)

- Consist 2 or more OR terms that are AND together.

- Ex: (A+B∓C)(A+C)

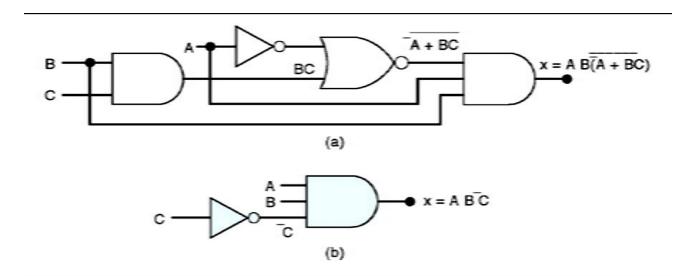

# Analysis of Logic Circuits

- First obtain one expression for the circuit, then try to simplify.

- Example:

- Two methods for simplifying:

- Algebraic method (use Boolean algebra theorems)

- Karnaugh mapping method (systematic, step-by-step approach)

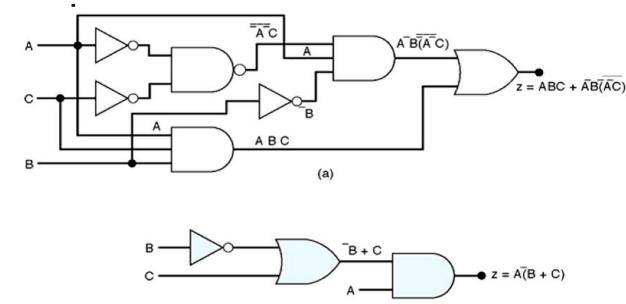

# **Algebraic Simplification**

- 1. Put the original expression into SOP form by repeated application of *DeMorgan's theorems*

- 2. Once in SOP form, check for *common factors* and factor whenever possible.

Example:

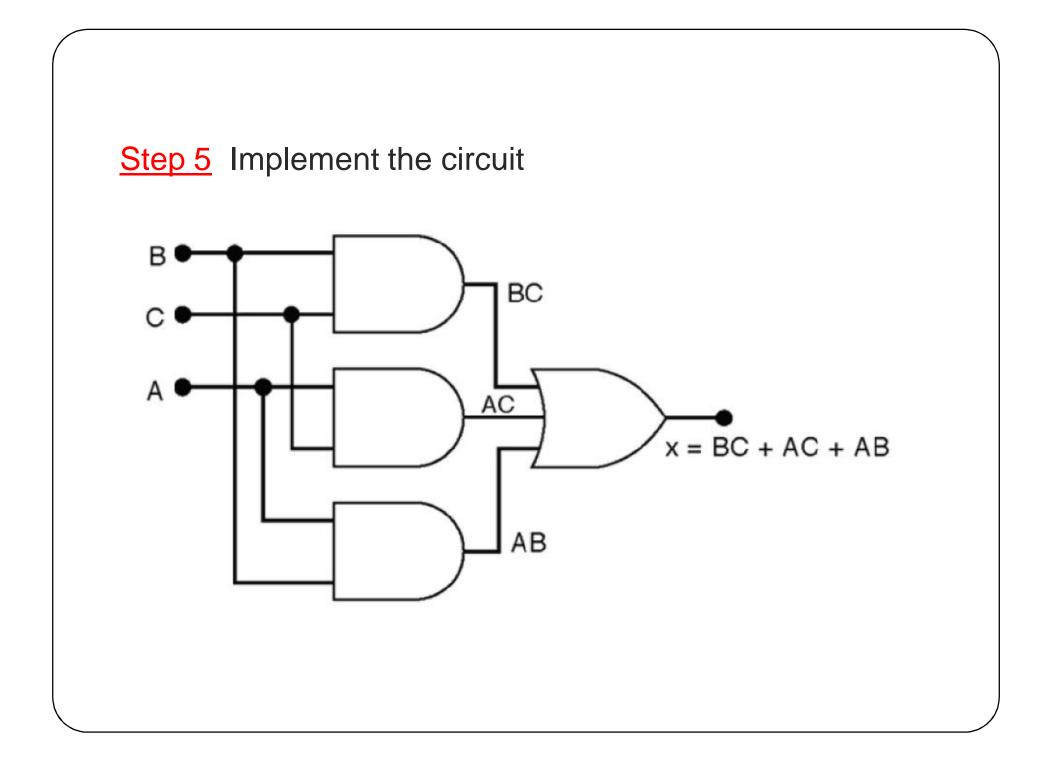

Step 3Write the SOP form the outputStep 4Simplify the output expression

$$x = \overline{ABC} + \overline{ABC} + A\overline{BC} + AB\overline{C} + ABC$$

$$x = \overline{ABC} + ABC + A\overline{BC} + AB\overline{C} + AB\overline{C} + AB\overline{C} + ABC$$

$$= BC(\overline{A} + A) + AC(\overline{B} + B) + AB(\overline{C} + C)$$

$$= BC + AC + AB$$

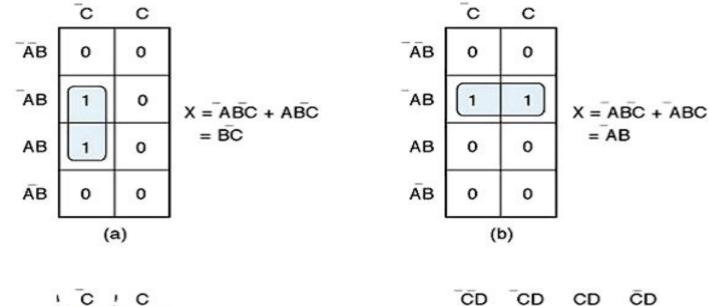

# Karnaugh Map (K-Map) Method

- K Map shows the relationship between inputs & outputs

- Horizontally & vertically adjacent squares differ only in one variable.

|     |   |                                            |                              |      | c   | С    |

|-----|---|--------------------------------------------|------------------------------|------|-----|------|

| AB  | C | X                                          |                              | [    | 907 | 3500 |

| 0 0 | 0 | 1 → ABC                                    |                              | AB   | 1   | 1    |

| 0 0 | 1 | $1 \rightarrow ABC$<br>$1 \rightarrow ABC$ |                              | ł    |     |      |

| 0 1 | 0 | 1 → ABC                                    | ( )                          | AB   | 1   | 0    |

| 0 1 | 1 | 0                                          | X = ABC + ABC<br>+ ABC + ABC |      |     |      |

| 1 0 | 0 | 0                                          | + ABC + ABC                  | A.B. |     |      |

| 10  | 1 | 0                                          | . ,                          | AB   | 1   | 0    |

| 1 1 | 0 | 1 → ABC                                    |                              |      |     |      |

| 1 1 | 1 | 0                                          |                              | ĀB   | 0   | 0    |

| Α | В | С | D | X        |                                  |       |    |    |    |    |

|---|---|---|---|----------|----------------------------------|-------|----|----|----|----|

| 0 | 0 | 0 | 0 | 0        |                                  |       | CD | CD | CD | ĊD |

| 0 | 0 | 0 | 1 | 1 → ABCD |                                  |       |    |    |    |    |

| 0 | 0 | 1 | 0 | 0        |                                  | AB    | 0  | 1  | 0  | 0  |

| 0 | 0 | 1 | 1 | 0        |                                  |       |    |    |    |    |

| 0 | 1 | 0 | 0 | 0        | ( ]                              | AB    | 0  | 1  | 0  | 0  |

| 0 | 1 | 0 | 1 | 1 → ABCD | X = ABCD + ABCD<br>+ ABCD + ABCD |       | -  |    |    |    |

| 0 | 1 | 1 | 0 | 0        | + ABCD + ABCD                    | 40    | •  | 4  |    | •  |

| 0 | 1 | 1 | 1 | 0        |                                  | AB    | 0  | 1  | 1  | 0  |

| 1 | 0 | 0 | 0 | 0        |                                  | 24.00 |    |    |    |    |

| 1 | 0 | 0 | 1 | 0        |                                  | ĀΒ    | 0  | 0  | 0  | 0  |

| 1 | 0 | 1 | 0 | 0        |                                  | 2     |    |    |    |    |

| 1 | 0 | 1 | 1 | 0        |                                  |       |    |    |    |    |

| 1 | 1 | 0 | 0 | 0        |                                  |       |    |    |    |    |

| 1 | 1 | 0 | 1 | 1 → ABCD |                                  |       |    |    |    |    |

| 1 | 1 | 1 | 0 | 0        |                                  |       |    |    |    |    |

| 1 | 1 | 1 | 1 | 1 → ABCD |                                  |       |    |    |    |    |

(c)

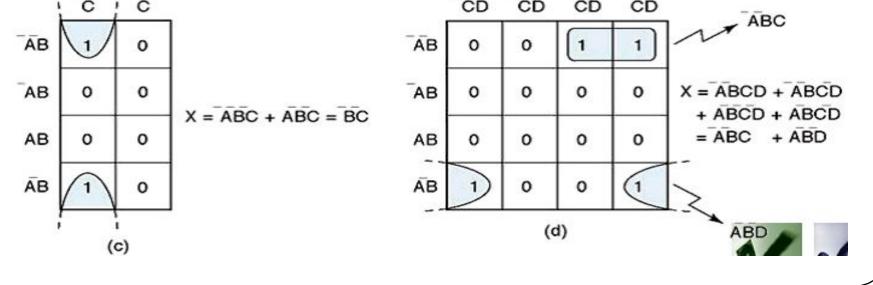

#### Looping is a process combining the squares which contain 1s. The output expression can be simplified by looping.

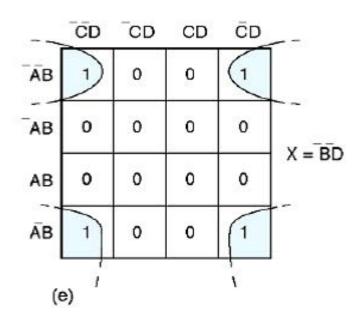

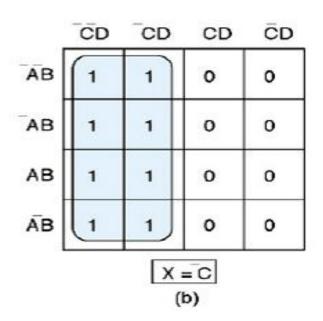

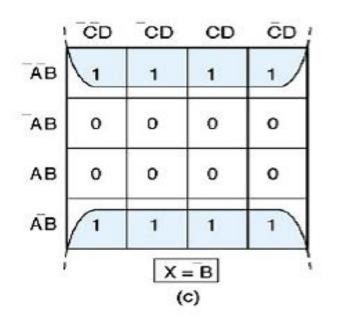

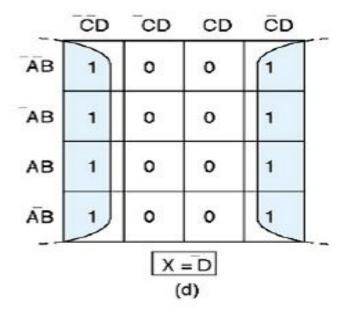

CD CD CD CD AB AB AB AB X = B (a)

#### Rule for loops of any size

When a variable appears in both complemented & uncomplemented form within a loop, that variable is eliminated from the expression. Variables that are the same for all squares of the loop must appear in the final expression.

#### **Complete Simplification Process**

- 1.Construct the K map and place 1s and 0s in the squares according to the truth table.

- 2.Loop the isolated 1s which are not adjacent to any other 1s. (single loops)

- 3.Loop any pair which contains a 1 adjacent to only one other 1. (double loops)

- 4.Loop any octet even if it contains one or more 1s that have already been looped.

- 5.Loop any quad that contains one or more 1s that have not already been looped, making sure to use the minimum number of loops.

- 6.Loop any pairs necessary to include any 1s that have not yet been looped, making sure to use the minimum number of loops.

- 7. Form the OR sum of all the terms generated by each loop.

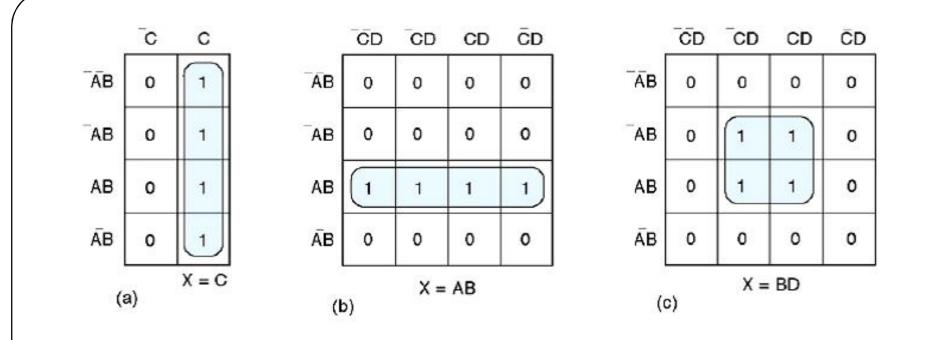

CD ĈD CD CD 1) AB 0 0 0 3 1 2 0 AB 0 1 1 X = ABCD ACD BD + + 5 6 7 8 AB 0 0 1 1 loop loop 6, loop 4 9 12 10 11, 15 7, 10, 11 AB 0 0 0 1 15 16 13 14 (a) CD ĈD CD CD AB 0 0 0 1 AB 1 1 1 1 BC X = ABACD 5 6 8 0 AB 1 0 1 loop 5. loop 5. loop 10 11 9 12 6.7.8 6.9.10 3.7 AB 0 0 0 0 16 13 14 15 (b) CD CD СD CD AB 0 0 0 1 з AB (1 1) 0 1 X =ABC ACD ABC ACD 5 8 + 6 + 7 1) AB 1 1 0 9,10 11, 15 2,6 7,8 9 10 11 12 AB 0 1 0 0 16 13 14 15 (c)

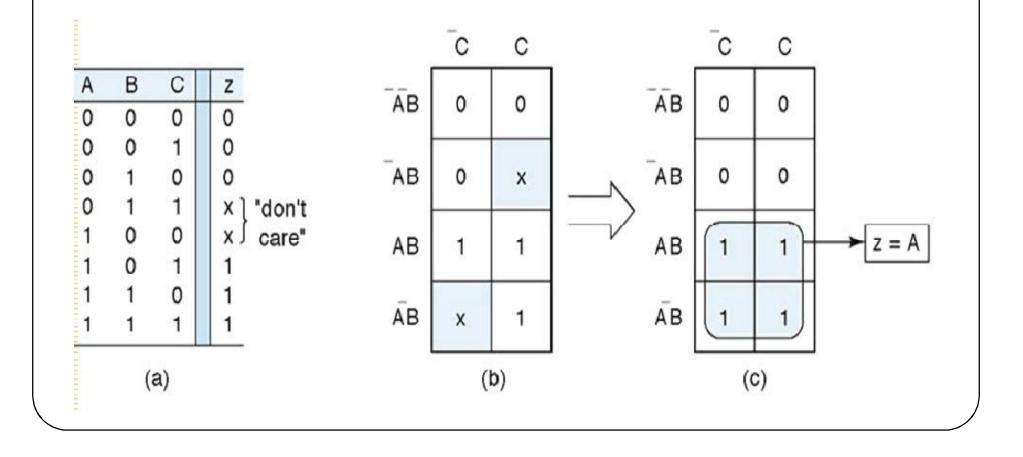

"Don't-Care" Conditions are certain input conditions for which there are no specified output levels. "Don't-care" conditions should be changed to either 0 or 1 to produce K-map looping that yields the simplest expression.

# Filling K-Map from Output Expression

When the desired output is presented as a Boolean expression instead of a truth table, the K map can be filled by using the following steps:

- 1. Get the expression into SOP form if it is not already so.

- 2. For each product term in the SOP expression, place a 1 in each K-map square whose label contains the same combination of input variables. Place a 0 in all other squares.

- Don't care condition can come about for several reasons:

- In some situations certain input combination can never occur and so there is no specified output for these condition.

- Whenever don't care conditions occur, we must decide which x to change to 0 and which to 1 to produce the best K-map looping (i.e the simplest expression)

#### Example

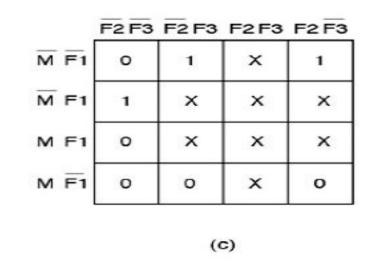

| М | F1 | F2 | F3 | OPEN |

|---|----|----|----|------|

| 0 | 0  | 0  | 0  | 0    |

| 0 | 0  | 0  | 1  | 1    |

| 0 | 0  | 1  | 0  | 1    |

| 0 | 0  | 1  | 1  | ×    |

| 0 | 1  | 0  | 0  | 1    |

| 0 | 1  | 0  | 1  | ×    |

| 0 | 1  | 1  | 0  | ××   |

| 0 | 1  | 1  | 1  | X    |

| 1 | 0  | 0  | 0  | 0    |

| 1 | 0  | 0  | 1  | 0    |

| 1 | 0  | 1  | 0  | 0    |

| 1 | 0  | 1  | 1  | ×    |

| 1 | 1  | 0  | 0  | 0    |

| 1 | 1  | 0  | 1  | X    |

| 1 | 1  | 1  | 0  | ××   |

| 1 | 1  | 1  | 1  | X    |

(a)

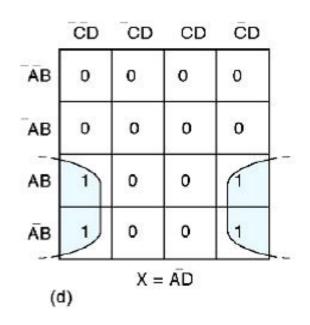

## Example

A BCD counter produces a four bit output representing the BCD code for the number of pulses hat have been applied to the counter input. For example, after 4 pulses have occurred, the counter outputs are DCBA= 01002 = 410. The counter resets to 0000 on the tenth pulse and starts counting over again. In other words, the DCBA output will never represent a number greater than 10012=910. Design the logic circuit that produces a HIGH output whenever the count is 2,3, or 9. Use K mapping and take advantage of the don't care conditions.

#### Summary

- Compared to the algebraic method, the K-map process is a more orderly process requiring fewer steps and always producing a minimum expression.

- For the circuits with large numbers of inputs (larger than four), other more complex techniques are used.

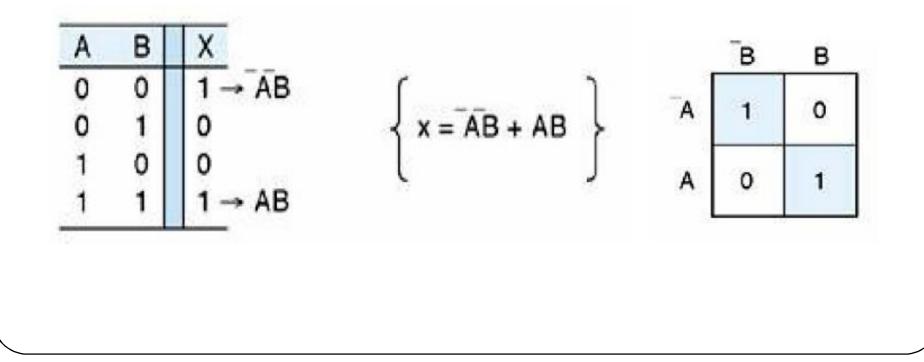

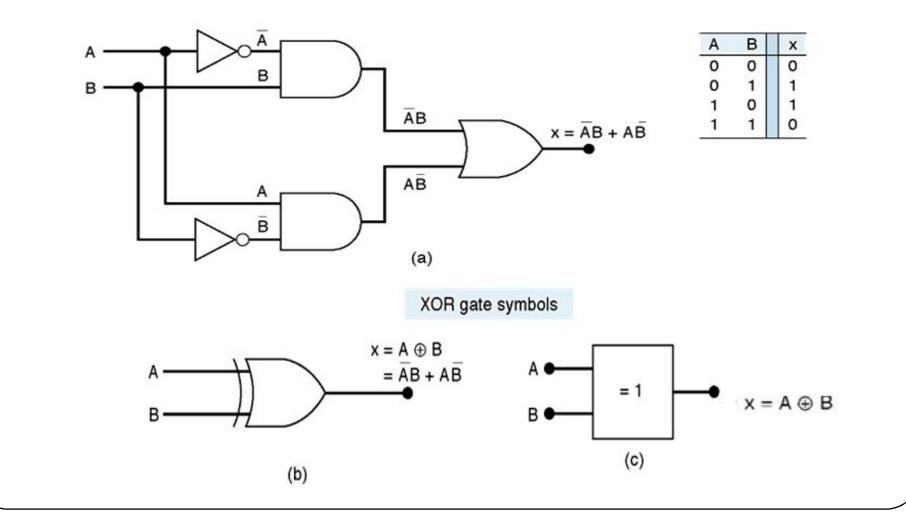

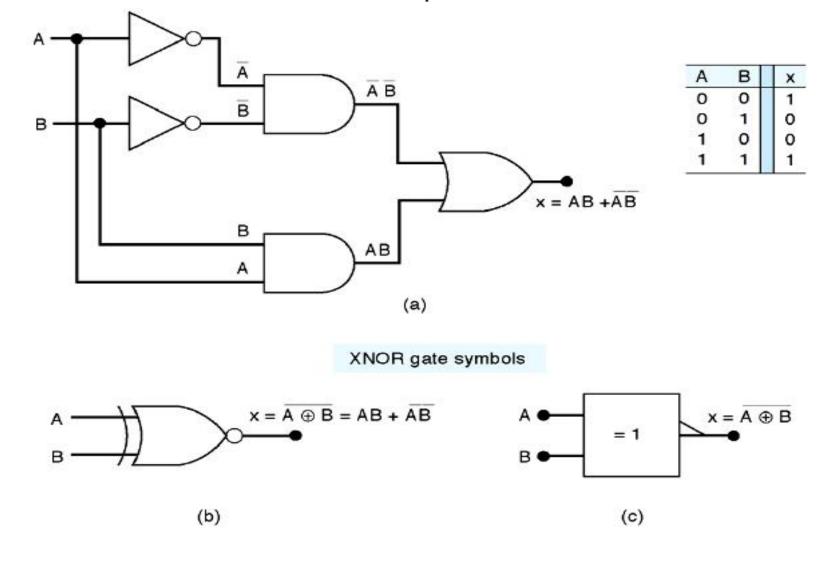

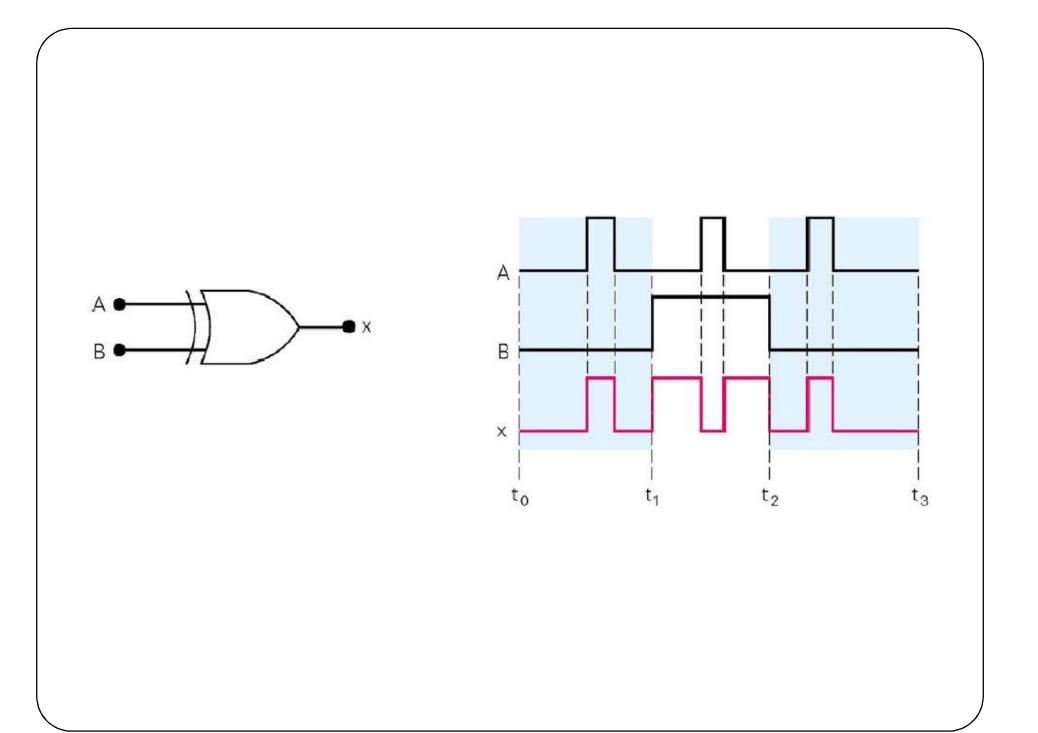

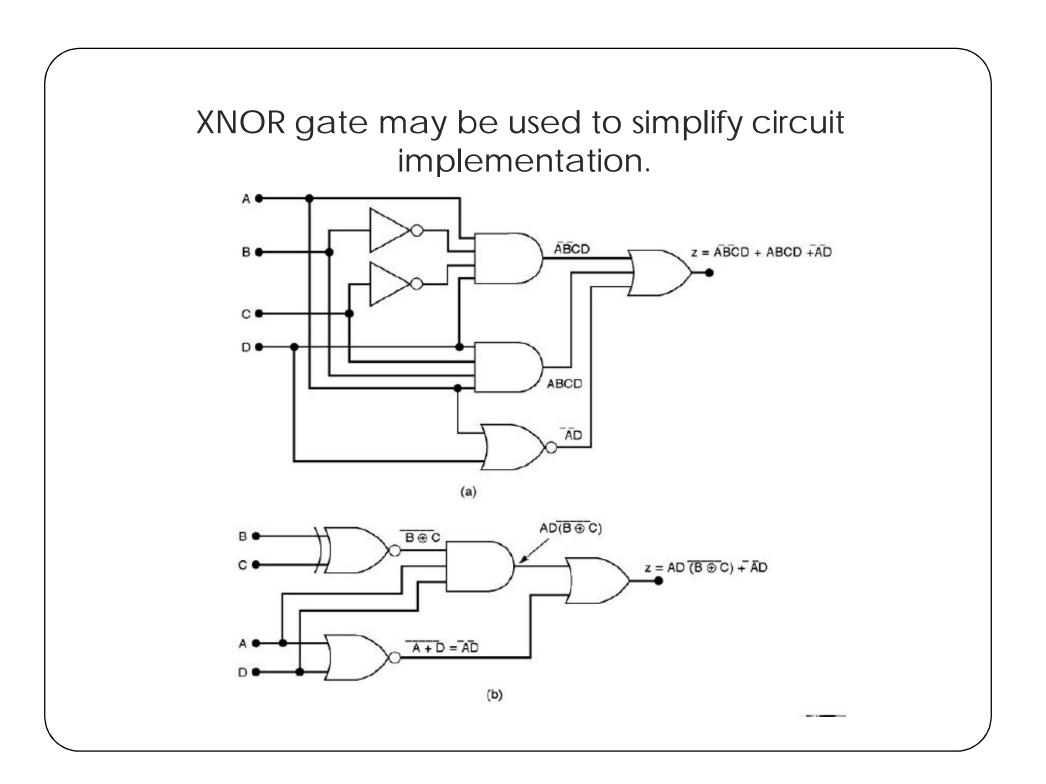

#### **Exclusive-OR and Exclusive-NOR Circuits**

Exclusive-OR (XOR) produces a HIGH output whenever the two inputs are at opposite levels.

Exclusive-NOR (XNOR) produces a HIGH output whenever the two inputs are at the same level.

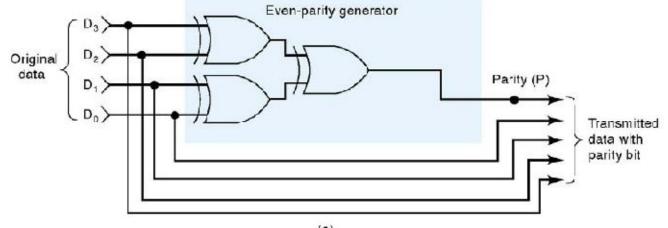

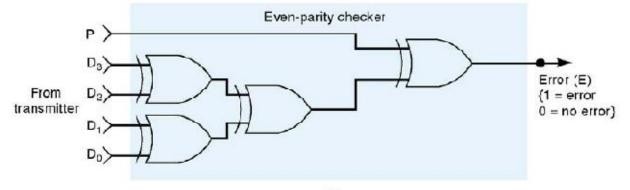

### **Parity Generator and Checker**

(b)

- A transmitter can attach a parity bit to a set of data bits before transmitting the data bits to a receiver. The receiver will detect any single bit errors that may have occurred during the transmission.

- In figure (a) the set of data to be transmitted is applied to the parity-generator circuit, which produces the even-parity bit, P, at its output. This parity bit is transmitted to the receiver along with the original data bits, making a total of five bits.

- In figure (b) these five bits (data+parity) enter the receiver's parity-checker circuit, which produces an error output, E that indicates whether or not a single-bit error has occurred.

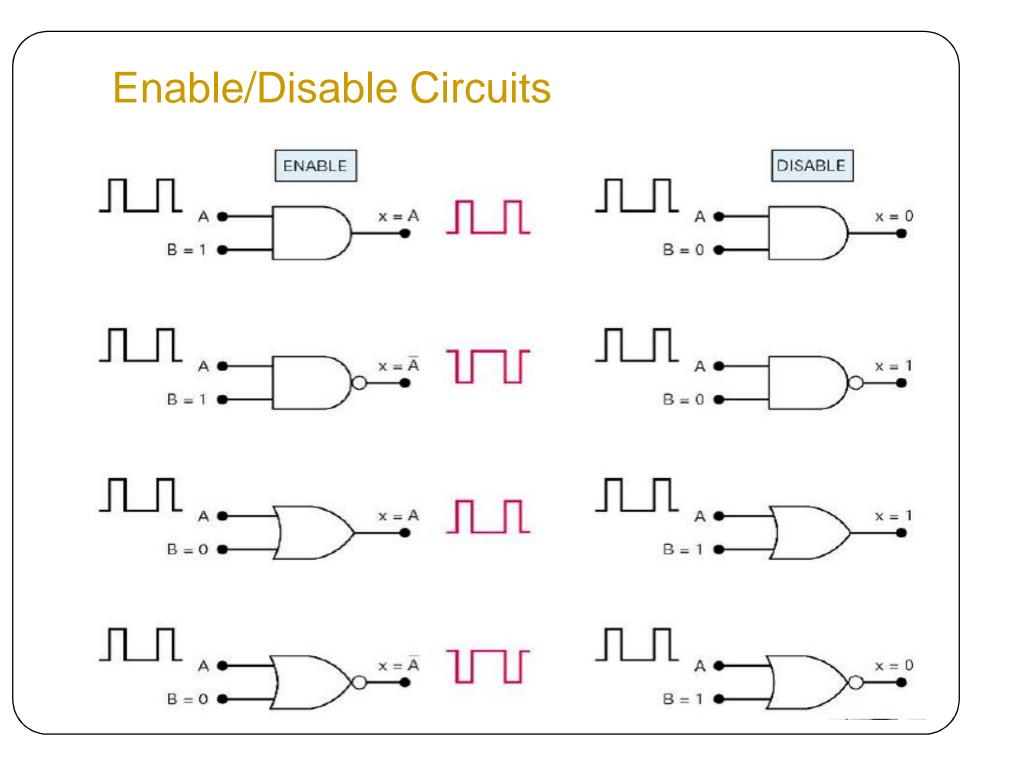

### Enable/Disable Circuits cont.

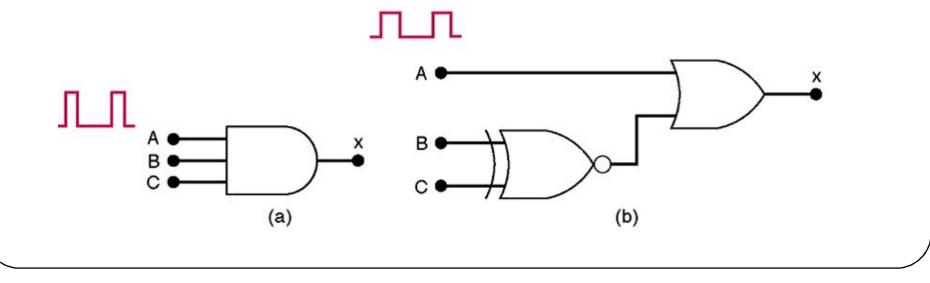

Ex. 1(Fig.a): Design a logic circuit that will allow a signal to pass to the output only when control inputs B and C are both HIGH; otherwise, the output will stay LOW.

Ex. 2(Fig.b): Design a logic circuit that will allow a signal to pass to the output only when one, but not both, of the control inputs are HIGH; otherwise, the output will stay LOW.

### **Basic Characteristics of Digital ICs**

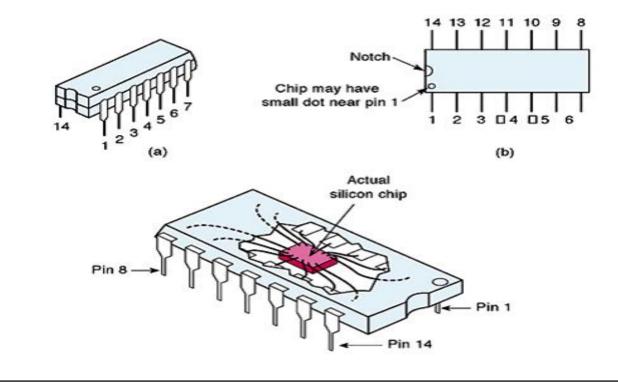

- Digital ICs (chips): a collection of resistors, diodes and transistors fabricated on a single piece of semiconductor materials called substrate.

- Dual-in-line package (DIP) is a common type of packages. It contains two parallel rows of pins.

Digital ICs are often categorized according to their circuit complexity as measured by the number of equivalent logic gates on the substrates. 6 levels of complexity:

SSI, MSI, LSI, VLSI, ULSI, GSI.

• SSI – having a small number of gates

### Assignment - 15

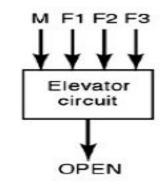

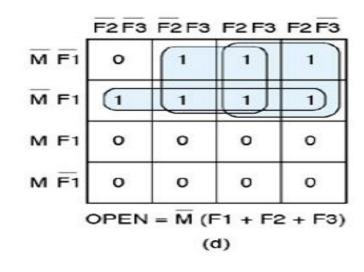

Design a logic circuit that controls an elevator door in a three-story building. The circuit has 4 inputs. M is a logic signal that indicates when the elevator is moving (M=1) or stop (M=1).F1, F2, F3 are floor indicator signals

that are normally LOW and they go HIGH only when the elevator is positioned at the level of that particular floor. For example, when the elevator is lined up level with the second floor, F2=1 and F1=F3=0. The circuit output is the open signal which is normally LOW and is to go HIGH when the elevator door is to be opened.